Difference between revisions of "Langage VHDL"

(→Description Project) |

|||

| (6 intermediate revisions by the same user not shown) | |||

| Line 18: | Line 18: | ||

* Windows Seven SP1 | * Windows Seven SP1 | ||

** Quartus II Version 9.1 SP2 | ** Quartus II Version 9.1 SP2 | ||

| + | |||

| + | === For Linux === | ||

| + | -> Simulateur pour compiler et exécuter du code VHDL <= non testé pour le moment | ||

| + | |||

| + | ** GHDL 0.37 (dernière release) | ||

== Description Project == | == Description Project == | ||

=== 7 Segment Display - DONE === | === 7 Segment Display - DONE === | ||

| − | ''In french :'' A l'aide d'une | + | ''In french :'' A l'aide d'une CPLD (EMP1270T144C5) et d'une carte électronique créée par l'ETML-ES, réalisation d'un schéma logique concernant l'affichage 7 segments (de 0 à F) sous Quartus et ensuite réaliser le code en VHDL. |

* 4 entrées correspondant à des switch | * 4 entrées correspondant à des switch | ||

* [FAIT] réalisation d'une table de vérité | * [FAIT] réalisation d'une table de vérité | ||

| Line 29: | Line 34: | ||

* [FAIT] Réalisation d'un code VHDL selon les équations trouvé avec les tables de Karnaugh | * [FAIT] Réalisation d'un code VHDL selon les équations trouvé avec les tables de Karnaugh | ||

| − | ''In English :'' With an electronics board created by the ETML-ES School and equiped with a | + | ''In English :'' With an electronics board created by the ETML-ES School and equiped with a CPLD, realization of logic schemtatics concerning the 7 Segments dispaly (0 to F) under Quartus and to write a VHDL Code. |

* 4 inputs : (switches) | * 4 inputs : (switches) | ||

* [DONE] Realization of a truth table | * [DONE] Realization of a truth table | ||

| Line 43: | Line 48: | ||

=== Jongleur === | === Jongleur === | ||

| − | ''In french :'' A l'aide d'une | + | ''In french :'' A l'aide d'une CPLD (EMP1270T144C5) et d'une carte électronique créée par l'ETML-ES, réalisation / simulation d'un jongleur à l'aide des deux affichage 7 segments à disposition. |

* Les segments '''A''' / '''E''' / '''F''' de l'affichage 7Seg_A seront utilisés | * Les segments '''A''' / '''E''' / '''F''' de l'affichage 7Seg_A seront utilisés | ||

| Line 56: | Line 61: | ||

* [FAIT] avec le Switch S9 de la carte, une pression (> 1s) doit permettre d'arrêter la séquence, de la redémarrer dans l'autre sens, si on appuie à nouveau la séquence s'arrête, si on appuie encore une fois al séquence repart dans la sens initial | * [FAIT] avec le Switch S9 de la carte, une pression (> 1s) doit permettre d'arrêter la séquence, de la redémarrer dans l'autre sens, si on appuie à nouveau la séquence s'arrête, si on appuie encore une fois al séquence repart dans la sens initial | ||

| − | ''In English :'' With an electronics board created by the ETML-ES School and equiped with a | + | ''In English :'' With an electronics board created by the ETML-ES School and equiped with a CPLD, realization / Simulation of a juggler with the both 7 Segments Display |

* Segments '''A''' / '''E''' / '''F''' of Display A will be used | * Segments '''A''' / '''E''' / '''F''' of Display A will be used | ||

| Line 70: | Line 75: | ||

=== Joyeux Noel - DONE === | === Joyeux Noel - DONE === | ||

| − | ''IN FRENCH'' A l'aide d'une | + | ''IN FRENCH'' A l'aide d'une CPLD (EMP1270T144C5) et d'une carte électronique créée par l'ETML-ES, réalisation / simulation d'un message défilant à l'aide deux affichage 7 segments à disposition. |

* [FAIT] lire un tableau contenant un message et le faire afficher sur les deux affichage A & B | * [FAIT] lire un tableau contenant un message et le faire afficher sur les deux affichage A & B | ||

* [FAIT] La valeur du segment B se déplacera sur le segment A, la valeur sur le segment disparaitra | * [FAIT] La valeur du segment B se déplacera sur le segment A, la valeur sur le segment disparaitra | ||

* [FAIT] le déplacement du message sera de 500ms (2Hz) | * [FAIT] le déplacement du message sera de 500ms (2Hz) | ||

| − | ''In English :'' With an electronics board created by the ETML-ES School and equiped with a | + | ''In English :'' With an electronics board created by the ETML-ES School and equiped with a CPLD, realization / Simulation of the VHDL code which allows to read a table and to display a message on two 7 Segments Display |

* [DONE] read a table including a message and to display this message on two 7 Segments Display | * [DONE] read a table including a message and to display this message on two 7 Segments Display | ||

* [DONE] the Segment value (B) will moving on the segment B -> and the Segment value A will dispear | * [DONE] the Segment value (B) will moving on the segment B -> and the Segment value A will dispear | ||

| Line 81: | Line 86: | ||

=== Compteur 0 à 9 - DONE === | === Compteur 0 à 9 - DONE === | ||

| − | ''In french :'' A l'aide d'une | + | ''In french :'' A l'aide d'une CPLD (EMP1270T144C5) et d'une carte électronique créée par l'ETML-ES, réalisation d'un programme en VHDL qui permet d'afficher sur un affichage 7 Segments les valeurs de 0 à 9. Deux switches vont permettre des sélectionner 4 fréquences d'horloges différentes (1Hz, 2Hz, 500Hz, 1kHz) et deux autres switches vont permettre de configurer le mode du compteur arrêt/marche + incrémente/décrémente |

* [FAIT] Réalisation de compteurs/diviseurs pour arriver au fréquence voulues | * [FAIT] Réalisation de compteurs/diviseurs pour arriver au fréquence voulues | ||

* [FAIT] Sélection de la fréquence voulue | * [FAIT] Sélection de la fréquence voulue | ||

| Line 89: | Line 94: | ||

* [FAIT] Programmation de la carte | * [FAIT] Programmation de la carte | ||

| − | ''In English :'' With an electronics board created by the ETML-ES School and equiped with a | + | ''In English :'' With an electronics board created by the ETML-ES School and equiped with a CPLD(EMP1270T144C5), realization program in VHDL which allows to display on 7SEG screen the values of 0 tto 9 (counter). Two switches will allow to select 4 different frequencies (1Hz, 2Hz, 500Hz, 1kHz) and two others will allow to configure the functional mode (START/STOP + increment/decrement counter) |

* [FAIT] counter/divisor for the desired frequency | * [FAIT] counter/divisor for the desired frequency | ||

* [FAIT] Selection of frequency | * [FAIT] Selection of frequency | ||

| Line 98: | Line 103: | ||

=== Effect Mirror on the 7 Segments === | === Effect Mirror on the 7 Segments === | ||

| − | ''In french :'' A l'aide d'une | + | ''In french :'' A l'aide d'une CPLD (EMP1270T144C5) et d'une carte électronique créée par l'ETML-ES, réalisation d'un programme en VHDL qui permet d'afficher sur deux affichages 7 Segments les valeurs de A é D. Deux switches vont permettre des sélectionner 4 modes : NORMAL - HORIZONTAL - VERTICAL - PAS D AFFICHAGE. |

* [FAIT] Réalisation d'un composant - gestion d'affichage | * [FAIT] Réalisation d'un composant - gestion d'affichage | ||

* [FAIT] Réalisation d'un composant - gestion compteur d'etat | * [FAIT] Réalisation d'un composant - gestion compteur d'etat | ||

* [FAIT] gestion d'un compteur/diviseur pour horloge | * [FAIT] gestion d'un compteur/diviseur pour horloge | ||

| − | ''In English :''With an electronics board created by the ETML-ES School and equiped with a | + | ''In English :''With an electronics board created by the ETML-ES School and equiped with a CPLD(EMP1270T144C5), realization program in VHDL which allows to display on 7SEG screen the values of A to D, the first degment displays normaly the value, and on the second display allows to see the letter inverted either horizontal or vertical. Two switches will allow to select 4 different mode : NORMAL - HORIZONTAL - VERTCIAL - NO DISPLAY. |

* [DONE] Realization component - displays managment | * [DONE] Realization component - displays managment | ||

* [DONE] Realization component - stats counter managment | * [DONE] Realization component - stats counter managment | ||

| Line 109: | Line 114: | ||

=== CADENAS V0.3 - DONE === | === CADENAS V0.3 - DONE === | ||

| − | ''In french :'' A l'aide d'une | + | ''In french :'' A l'aide d'une CPLD (EMP1270T144C5) et d'une carte électronique créée par l'ETML-ES, réalisation d'un programme en VHDL qui permet de simuler l'ouverture d'un cadenas. 2 Switches sont utilisés pour les 3 modes : un mode de repos / un mode de mémorisation d'un nouveau code / un mode de lecture. 4 switches permettent l'enregistrement d'un nouveau code ou au contraire de pouvoir lire le code. |

* [FAIT] Réalisation d'un seul process en mode case qui gère l'affichage, les leds et le nouveau code | * [FAIT] Réalisation d'un seul process en mode case qui gère l'affichage, les leds et le nouveau code | ||

* [FAIT] Simulation | * [FAIT] Simulation | ||

* [FAIT] Programmation de la carte | * [FAIT] Programmation de la carte | ||

| − | ''In English :''With an electronics board created by the ETML-ES School and equiped with a | + | ''In English :''With an electronics board created by the ETML-ES School and equiped with a CPLD(EMP1270T144C5), realization program in VHDL which allows to simulate the behavior of a padlock. 2 switches are used to 3 modes : rest / recording the new code / reading. 4 switches allow to record a new code or to read the code |

| − | * [ | + | * [DONE] Realization with one process (case) of the display part, management leds, management code |

| − | * [ | + | * [DONE] Simulation |

| − | * [ | + | * [DONE] Programming the board |

== Project Source == | == Project Source == | ||

| Line 197: | Line 202: | ||

=== lien WEB === | === lien WEB === | ||

* [https://en.wikipedia.org/wiki/List_of_HDL_simulators HDL SIMULATOR - English] | * [https://en.wikipedia.org/wiki/List_of_HDL_simulators HDL SIMULATOR - English] | ||

| + | * [https://fr.wikibooks.org/wiki/TD3_VHDL_Compteurs_et_registres Wiki sur les compteurs & les registres] | ||

| + | * [https://fr.wikibooks.org/wiki/TD1_VHDL Notion de notion concurrente et séquentielle] | ||

| + | * [http://amouf.chez.com/syntaxe.htm#OPERATOR synthaxe VHDL] | ||

* [http://www.csee.umbc.edu/portal/help/VHDL/stdpkg.html STANDART PACKAGE - English] | * [http://www.csee.umbc.edu/portal/help/VHDL/stdpkg.html STANDART PACKAGE - English] | ||

* [http://hdl.telecom-paristech.fr/vhdl_structurel.html#base Creation composant - Français] | * [http://hdl.telecom-paristech.fr/vhdl_structurel.html#base Creation composant - Français] | ||

* [http://jacques.weber.pagesperso-orange.fr/vhdl_html/Vhdl.htm#hexadécimal Résumé VHDL - Français] | * [http://jacques.weber.pagesperso-orange.fr/vhdl_html/Vhdl.htm#hexadécimal Résumé VHDL - Français] | ||

| − | * [http:// | + | * [http://jacques.weber.pagesperso-orange.fr/sources/index.htm#sites Lien sur le livre "le langage VHDL" - Jacquees Weber] |

| − | * [https:// | + | * [https://github.com/ghdl/ghdl Simulateur et compilateur de code VHDL sous linux / Windows / Mac] |

| − | + | ||

=== lien PDF === | === lien PDF === | ||

| Line 213: | Line 220: | ||

* [https://fixme.ch/wiki/File:Compteur_vhdl.pdf explication creation compteur] | * [https://fixme.ch/wiki/File:Compteur_vhdl.pdf explication creation compteur] | ||

* [https://fixme.ch/wiki/Fpga page FPGA - Fixme] | * [https://fixme.ch/wiki/Fpga page FPGA - Fixme] | ||

| + | |||

| + | == Conf == | ||

| + | * [https://www.twitch.tv/fixme_hs stremaing live de la conf] | ||

| + | * [https://youtu.be/MDdDgHM0GYk vidéo disponible sur Youtube] | ||

| + | * Slides de présentation lors de la conf[[https://fixme.ch/w/images/0/0f/Presentation_VHDL_Ta_Mere.pdf Slide_Conf_VHDL]] | ||

== Participant == | == Participant == | ||

* [[User:Philoux]] | * [[User:Philoux]] | ||

* you !!??!! | * you !!??!! | ||

Latest revision as of 00:23, 19 November 2021

Contents

Description

In french :

En se basant sur des livres sur le VHDL, des supports de cours ou sur le net directement, ce wiki a pour but de montrer des exemples de codes réalisés sur des plaques d'évaluation.

L'onglet discussion peut être fort intéressant concernant des astuces, questions, problèmes rencontrés lors de développement en VHDL. Alors n'hésiter pas à compléter ce wiki et la page discussion et le projet "GITHUB" qui lui sera associé :-)

In English:

Based on the VHDL Books, cours support or links on the net, this wiki has for goal to show some VHDL examples releazied on experimental board.

Development Environment

For Windows

-> Dev environment for Philou :

- Windows Seven SP1

- Quartus II Version 9.1 SP2

For Linux

-> Simulateur pour compiler et exécuter du code VHDL <= non testé pour le moment

- GHDL 0.37 (dernière release)

Description Project

7 Segment Display - DONE

In french : A l'aide d'une CPLD (EMP1270T144C5) et d'une carte électronique créée par l'ETML-ES, réalisation d'un schéma logique concernant l'affichage 7 segments (de 0 à F) sous Quartus et ensuite réaliser le code en VHDL.

- 4 entrées correspondant à des switch

- [FAIT] réalisation d'une table de vérité

- [FAIT] simplification de la table de vérité par karnaugh et trouvé les équations logiques

- [FAIT] réalisation du schéma logique sous Quatrus

- [FAIT] Simulation avec Quartus

- [FAIT] Réalisation d'un code VHDL selon les équations trouvé avec les tables de Karnaugh

In English : With an electronics board created by the ETML-ES School and equiped with a CPLD, realization of logic schemtatics concerning the 7 Segments dispaly (0 to F) under Quartus and to write a VHDL Code.

- 4 inputs : (switches)

- [DONE] Realization of a truth table

- [DONE] simplification of the truth table by Karnaugh table and found the logic equation

- [DONE] Realization of logic schematics (Quartus)

- [DONE] Simulation with Quartus

- [DONE] realization VHDL code according the Karnaugh Table

Jongleur

In french : A l'aide d'une CPLD (EMP1270T144C5) et d'une carte électronique créée par l'ETML-ES, réalisation / simulation d'un jongleur à l'aide des deux affichage 7 segments à disposition.

- Les segments A / E / F de l'affichage 7Seg_A seront utilisés

- Les segments A / B / C de l'affichage 7Seg_B seront utilisés

- Utilisation du PEC12 pour lancement du jonglage

- Reset pour arrêter le jonglage

- 4 switches utilisés pour le mode de Jonglage

- PEC12 pour le choix de la vitesse (allant de 0,5 Hz à 2 Hz)

=> travail en cours

- [FAIT] Réalisé un compteur de 2Hz et faire tourner les segment dans le sens des aiguilles d'une montre (sens de F1 -> E1 -> A1 -> A2 -> B2 -> C1... en on recommence)

- [FAIT] avec le Switch S9 de la carte, une pression (> 1s) doit permettre d'arrêter la séquence, de la redémarrer dans l'autre sens, si on appuie à nouveau la séquence s'arrête, si on appuie encore une fois al séquence repart dans la sens initial

In English : With an electronics board created by the ETML-ES School and equiped with a CPLD, realization / Simulation of a juggler with the both 7 Segments Display

- Segments A / E / F of Display A will be used

- Segments A / B / C of Display B will be used

- Using of PEC12 to start the juggling

- Reset to stop the juggling

- 4 switches used for the mode of juggling

- PEC12 to use the speed choice of juggling (to 0,5 Hz at 2 Hz)

=> work in progress

- [DONE] Realized a cycle counter of 2Hz to do turned the segments in clockwise (Way: F1 -> E1 -> A1 -> A2 -> B2 -> C1... it is continuous

- [DONE] With a push (> 1s) on the S9 Switch, the cycle must stopped if after a new push on this button, the cycle must be the opposite at the first, if a new push again the cylce must stopped and to finish if still a push, the cycle set out again at the start cycle.

Joyeux Noel - DONE

IN FRENCH A l'aide d'une CPLD (EMP1270T144C5) et d'une carte électronique créée par l'ETML-ES, réalisation / simulation d'un message défilant à l'aide deux affichage 7 segments à disposition.

- [FAIT] lire un tableau contenant un message et le faire afficher sur les deux affichage A & B

- [FAIT] La valeur du segment B se déplacera sur le segment A, la valeur sur le segment disparaitra

- [FAIT] le déplacement du message sera de 500ms (2Hz)

In English : With an electronics board created by the ETML-ES School and equiped with a CPLD, realization / Simulation of the VHDL code which allows to read a table and to display a message on two 7 Segments Display

- [DONE] read a table including a message and to display this message on two 7 Segments Display

- [DONE] the Segment value (B) will moving on the segment B -> and the Segment value A will dispear

- [DONE] the message moving will be of 500ms (2Hz)$

Compteur 0 à 9 - DONE

In french : A l'aide d'une CPLD (EMP1270T144C5) et d'une carte électronique créée par l'ETML-ES, réalisation d'un programme en VHDL qui permet d'afficher sur un affichage 7 Segments les valeurs de 0 à 9. Deux switches vont permettre des sélectionner 4 fréquences d'horloges différentes (1Hz, 2Hz, 500Hz, 1kHz) et deux autres switches vont permettre de configurer le mode du compteur arrêt/marche + incrémente/décrémente

- [FAIT] Réalisation de compteurs/diviseurs pour arriver au fréquence voulues

- [FAIT] Sélection de la fréquence voulue

- [FAIT] Gestion du mode comptage/décomptage

- [FAIT] Gestion de l'affichage 7 Segment

- [FAIT] Simulation avec Quartus

- [FAIT] Programmation de la carte

In English : With an electronics board created by the ETML-ES School and equiped with a CPLD(EMP1270T144C5), realization program in VHDL which allows to display on 7SEG screen the values of 0 tto 9 (counter). Two switches will allow to select 4 different frequencies (1Hz, 2Hz, 500Hz, 1kHz) and two others will allow to configure the functional mode (START/STOP + increment/decrement counter)

- [FAIT] counter/divisor for the desired frequency

- [FAIT] Selection of frequency

- [FAIT] management mode (START/STOP + increment/decrement ccounter)

- [FAIT] Managment 7 Segments Display

- [FAIT] Simulation with Quartus

- [FAIT] Programming board

Effect Mirror on the 7 Segments

In french : A l'aide d'une CPLD (EMP1270T144C5) et d'une carte électronique créée par l'ETML-ES, réalisation d'un programme en VHDL qui permet d'afficher sur deux affichages 7 Segments les valeurs de A é D. Deux switches vont permettre des sélectionner 4 modes : NORMAL - HORIZONTAL - VERTICAL - PAS D AFFICHAGE.

- [FAIT] Réalisation d'un composant - gestion d'affichage

- [FAIT] Réalisation d'un composant - gestion compteur d'etat

- [FAIT] gestion d'un compteur/diviseur pour horloge

In English :With an electronics board created by the ETML-ES School and equiped with a CPLD(EMP1270T144C5), realization program in VHDL which allows to display on 7SEG screen the values of A to D, the first degment displays normaly the value, and on the second display allows to see the letter inverted either horizontal or vertical. Two switches will allow to select 4 different mode : NORMAL - HORIZONTAL - VERTCIAL - NO DISPLAY.

- [DONE] Realization component - displays managment

- [DONE] Realization component - stats counter managment

- [DONE] counter/divisor managment for clock

CADENAS V0.3 - DONE

In french : A l'aide d'une CPLD (EMP1270T144C5) et d'une carte électronique créée par l'ETML-ES, réalisation d'un programme en VHDL qui permet de simuler l'ouverture d'un cadenas. 2 Switches sont utilisés pour les 3 modes : un mode de repos / un mode de mémorisation d'un nouveau code / un mode de lecture. 4 switches permettent l'enregistrement d'un nouveau code ou au contraire de pouvoir lire le code.

- [FAIT] Réalisation d'un seul process en mode case qui gère l'affichage, les leds et le nouveau code

- [FAIT] Simulation

- [FAIT] Programmation de la carte

In English :With an electronics board created by the ETML-ES School and equiped with a CPLD(EMP1270T144C5), realization program in VHDL which allows to simulate the behavior of a padlock. 2 switches are used to 3 modes : rest / recording the new code / reading. 4 switches allow to record a new code or to read the code

- [DONE] Realization with one process (case) of the display part, management leds, management code

- [DONE] Simulation

- [DONE] Programming the board

Project Source

- https://github.com/fixme-lausanne/Langage-VHDL---Exemple-Codes

- https://github.com/philouxy/Langage-VHDL---Exemple-code-

VHDL Code

IN FRENCH: pour qu'un code VHDL soit au minium compilable/synthétisable, il faut qu'il ait un bloc d'entité (entity), une architecture et la déclaration de librairie (library).

IN ENGLISH: a VHDL code need 3 parts : 1/ declaration of libraries 2/ declaration of entity 3/ declaration of architecture

library

IN FRENCH: dans notre code VHDL pour que celui-ci puisse être compilé il faut ajouter une référence à une ou des librairies que nous voudrions utiliser.

IN ENGLISH: for that our VHDL code compiles, we need to use the different libraries, below the most library used.

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.numeric_std.all;

entity

IN FRENCH: il faut aussi une entité qui contiendra les ports (entrée / sortie), soit réel, soit lié à un composant interne au composant électronique

IN ENGLISH: then a entity must been implemented, this one includes the ports (input/output) either real or linked a the electronic internal componant

PORTS

IN FRENCH: Pour déclarer un port, il faut : UN NOM, UN MODE (in / out / inout), UN TYPE (bit / std_logic / bit_vector / std_logic_vector)

IN ENGLISH: To declare a port, it must : a NAME, a MODE (in / out / inout), a TYPE (bit / std_logic / bit_vector / std_logic_vector)

entity NOM_ENTITY is

port( -- délcaration ports IN/OUT

exemple_1 : in bit;

exemple_2 : out std_logic;

exemple_3 : inout std_logic_vector(3 downto 0)

);

end NOM_ENTITY;

architecture

IN FRENCH : l'architecture est le corps du programme, celui-ci est composé de la déclaration interne des signaux qui ne sont pas utilisés dans l'entité du programme, ensuite utiliser le mot clé begin et écrire le comportement du programmes // affectation // déclaration de process

IN ENGLISH : the architecture is the program body, this one makes up of internal signal's declaration not used in the entity. Then use the key word begin follow-up of program's behavior // allocation // process statment.

Exemple

architecture Architecture_name of Entity_name is // déclaration signaux interne begin //comportement systeme end Architecture_name;

TYPE / CONSTANT / SIGNAL

TABLE / TABLEAU

IN FRENCH : pour déclarer un tableau en VHDL, il faut d'abord déclarer un nouveau type en lui donnant un nom, le nombre de cases que composera le tableau et de savoir qu'elle sera la type de donner des différentes cases

IN ENGLISH : to declare a table in VHDL, it must give a new type with a name, describe the cell number which includes the table and to know the cell type.

Exemple

type NAME_OF_TABLE is array (0 to 9) of std_logic_vector(3 downto 0); -- le tableau comportera 10 cellule de type sdt_logic_vector de 4bits

compteur / counter

component

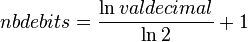

TRICKS/ASTUCES

IN FRENCH: pour connaître la taille binaire d'un nombre decimal utiliser la formule ci-dessous

IN ENGLISH: to know the binary size of decimal number, use the below

Link

lien WEB

- HDL SIMULATOR - English

- Wiki sur les compteurs & les registres

- Notion de notion concurrente et séquentielle

- synthaxe VHDL

- STANDART PACKAGE - English

- Creation composant - Français

- Résumé VHDL - Français

- Lien sur le livre "le langage VHDL" - Jacquees Weber

- Simulateur et compilateur de code VHDL sous linux / Windows / Mac

lien PDF

- -> PDF cours VHDL - Français

- -> PDF cours VHDL - Français

- -> PDF User Manuel de quartus II - Français

- -> PDF User Manuel de Quartus II - Français

lien interne

Conf

- stremaing live de la conf

- vidéo disponible sur Youtube

- Slides de présentation lors de la conf[Slide_Conf_VHDL]

Participant

- User:Philoux

- you !!??!!