Difference between revisions of "Talk:Langage VHDL"

| Line 42: | Line 42: | ||

constant VAL_X : std_logic_vector (19 downto 0) := to_stdlogicvector(x"EAE34"); -- ne marche pas | constant VAL_X : std_logic_vector (19 downto 0) := to_stdlogicvector(x"EAE34"); -- ne marche pas | ||

constant VAL_X : std_logic_vector (19 downto 0) := std_logic_vector(to_unsigned(x"EAE34",VAL_X'length)); -- ne marche pas | constant VAL_X : std_logic_vector (19 downto 0) := std_logic_vector(to_unsigned(x"EAE34",VAL_X'length)); -- ne marche pas | ||

| + | |||

| + | Correction: | ||

Merci pour les réponses de Rick et de Micheal sur la mailing liste de Fixme, voici sur Quartus, la déclaration qui fonctionne : | Merci pour les réponses de Rick et de Micheal sur la mailing liste de Fixme, voici sur Quartus, la déclaration qui fonctionne : | ||

Revision as of 23:51, 24 August 2016

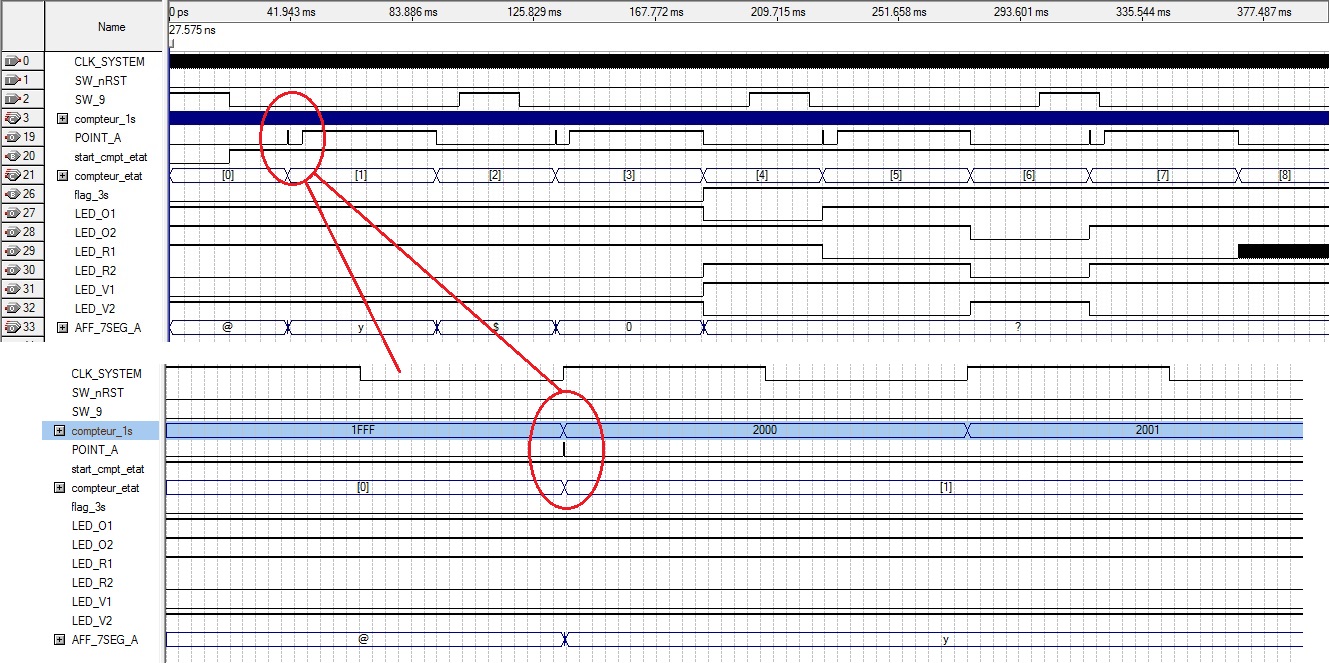

- PROJET GESTION FEU

=> avancement projet : en cours

=> problème rencontré :

1) sur la gestion des compteur, j'ai des glitch sur le signal que je crée à partir d'un compteur et je ne comprend pas l'erreur que je fais dans mon code. Pour le code, je l'ai mis sur le git (code VHDL) sous main_gestion_feux.vhd et antirebond.vhd

- PROJET 7 Segment Display

=> avancement projet : DONE

=> problème rencontré : 1) erreur de lecture ou retranscription de la table de vérité donc erreurs dans les équations

2) remarqué aussi qu'on ne peut pas passer de la schématique en VHDL par contre le contraire oui, d'un côté c'est évident car la synthétisation compile le code VHDL en schéma logique fait de portes, hmm

=> Date de modification : 28/07/2016

1) la table de vérité est juste, mais erreur dans la transcription schématique et dans les équations.

1a) correction :

Fa : A /B CD + A /(BCD) + /(AB) C /D + AB /C D

Fb : A /B C /D + /A BC + ABD + /A CD

Fd : /(AB) C /D + ABC + /A B /C D + A /(BCD)

Fg : /(AB) CD + ABC /D + /(BCD)

- PROJET JONGLEUR

=> avancement projet : en cours

=> Date de modification : 09/08/2016

=> problème rencontré :

1) Je n'arrive pas à trouver comment on peut insérer une valeur à constante lors de l'initialisation de celle-ci, je m'explique : j'aimerai utiliser une constante de 20bits (taille) donc un std_logic_vector, mais ça m’embête d'écrire 20bit car ca peut être source d'erreur ou si j'aimerai changer facilement, je peux par vraiment taper des 1 et des 0, donc j'ai essayé ces solutions d'écriture mais rien y...

constant VAL_X : std_logic_vector (19 downto 0) := x"EAE34" -- ne marche pas constant VAL_X : std_logic_vector (19 downto 0) := to_stdlogicvector(x"EAE34"); -- ne marche pas constant VAL_X : std_logic_vector (19 downto 0) := to_stdlogicvector(x"EAE34"); -- ne marche pas constant VAL_X : std_logic_vector (19 downto 0) := std_logic_vector(to_unsigned(x"EAE34",VAL_X'length)); -- ne marche pas

Correction:

Merci pour les réponses de Rick et de Micheal sur la mailing liste de Fixme, voici sur Quartus, la déclaration qui fonctionne :

constant VAL_X : std_logic_vector(19 downto 0) := To_stdlogicvector(X"EAE34");

attention, comme le langage VHDL est typé, la constante qui sera comparée par exemple à une variable (celle-ci devra être de la même taille) sinon ceci provoquera des erreurs.